# DP8212,DP8212M

DP8212 DP8212M 8-Bit Input/Output Port

Literature Number: SNOSBP8A

June 1988

# DP8212/DP8212M 8-Bit Input/Output Port

#### **General Description**

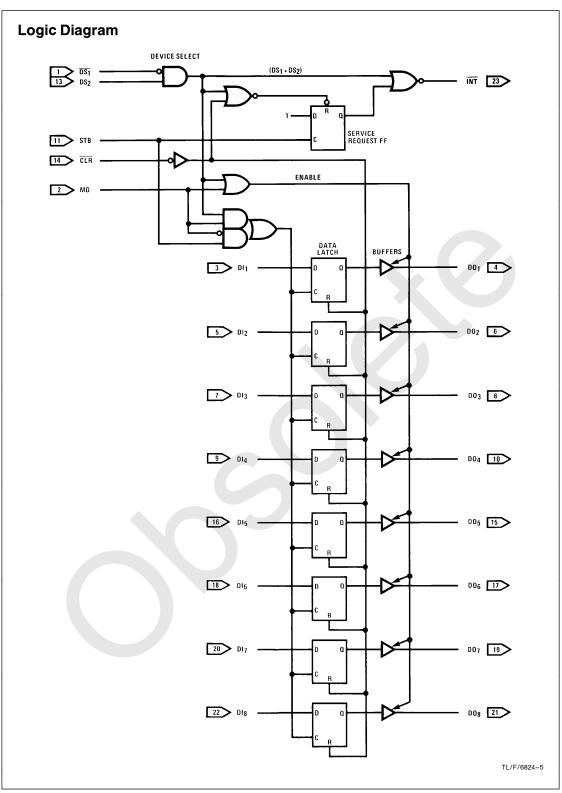

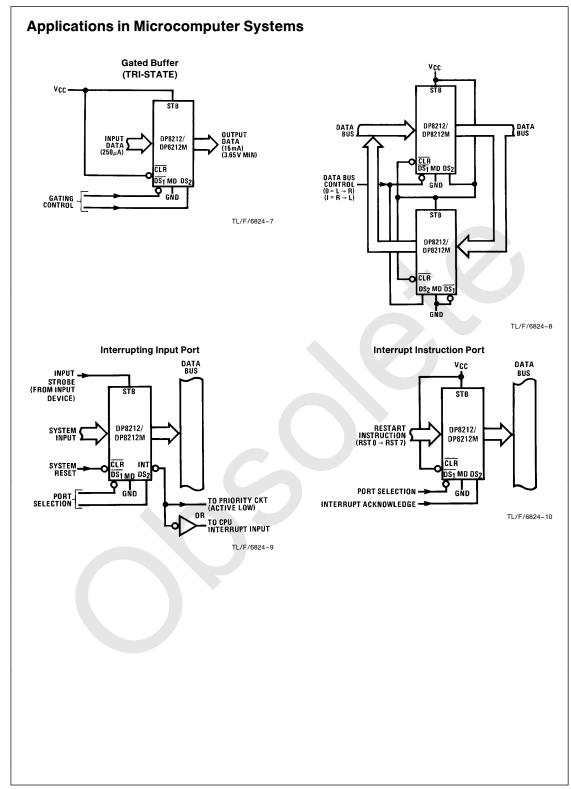

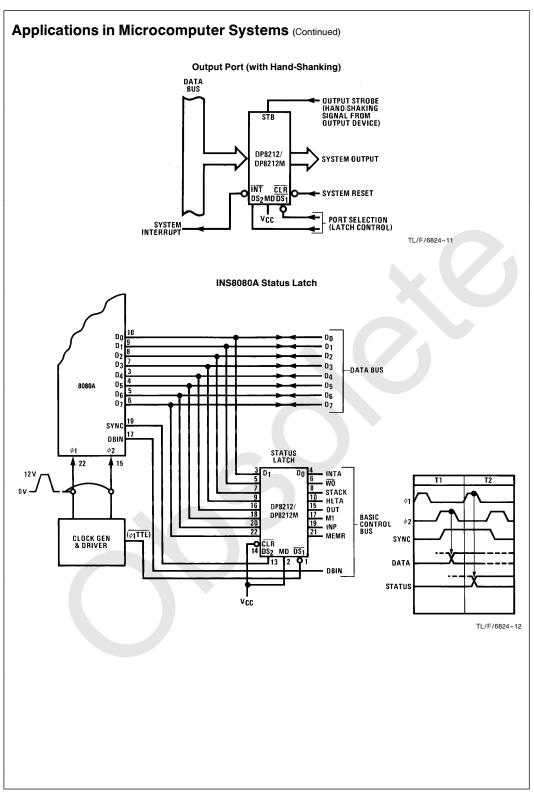

The DP8212/DP8212M is an 8-bit input/output port contained in a standard 24-pin dual-in-line package. The device, which is fabricated using Schottky Bipolar technology, is part of National Semiconductor's 8080A support family. The DP8212/DP8212M can be used to implement latches, gated buffers, or multiplexers. Thus, all of the major peripheral and input/output functions of a microcomputer system can be implemented with this device.

The DP8212/DP8212M includes an 8-bit latch with TRI-STATE® output buffers, and device selection and control logic. Also included is a service request flip-flop for the generation and control of interrupts to the microprocessor.

#### **Features**

- 8-Bit data latch and buffer

- Service request flip-flop for generation and control of interrupts

- 0.25 mA input load current

- TRI-STATE TTL output drive capability

- Outputs sink 15 mA

- Asynchronous latch clear

- 3.65V output for direct interface to INS8080A

- Reduces system package count by replacing buffers, latches, and multiplexers in microcomputer systems

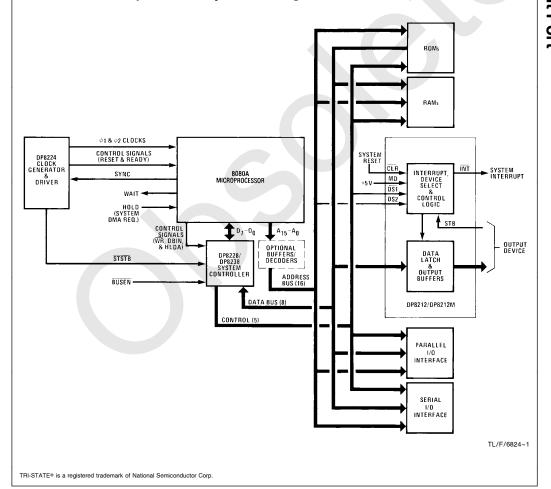

#### 8080A Microcomputer Family Block Diagram

## **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Storage Temperature -65°C to +160°C

All Output or Supply Voltages -0.5V to +7V

All Input Voltages -1.0V to 5.5V

Output Currents 125 mA

Maximum Power Dissipation\* at 25°C

Cavity Package 1903 mW Molded Package 2005 mW

## **Operating Conditions**

|                                        | Min  | Max  | Units    |

|----------------------------------------|------|------|----------|

| Supply Voltage (V <sub>CC</sub> )      |      |      |          |

| DP8212M                                | 4.50 | 5.50 | $V_{DC}$ |

| DP8212                                 | 4.75 | 5.25 | $V_{DC}$ |

| Operating Temperaure (T <sub>A</sub> ) |      |      |          |

| DP8212M                                | -55  | +125 | °C       |

| DP8212                                 | 0    | +75  | °C       |

Note: Maximum ratings indicate limits beyond which permanent damage may occur. Continuous operation at these limits is not intended and should be limited to those conditions specified under DC electrical characteristics.

## $\textbf{Electrical Characteristics} \ \ \mathsf{Min} \leq \mathsf{T}_A \leq \mathsf{Max}, \ \mathsf{Min} \leq \mathsf{V}_{CC} \leq \mathsf{Max}, \ \mathsf{unless} \ \mathsf{otherwise} \ \mathsf{noted}$

| Symbol          | Parameter                                                                       | Conditions                           |         | Min  | Тур | Max   | Units |

|-----------------|---------------------------------------------------------------------------------|--------------------------------------|---------|------|-----|-------|-------|

| lF              | Input Load Current,<br>STB, DS2, CLR, DI <sub>1</sub> -DI <sub>8</sub> Inputs   | $V_{F} = 0.45V$                      |         |      |     | -0.25 | mA    |

| lF              | Input Load Current, MD Input                                                    | $V_{F} = 0.45V$                      |         |      |     | -0.75 | mA    |

| IF              | Input Load Current, DS1 Input                                                   | $V_{F} = 0.45V$                      |         |      |     | -1.0  | mA    |

| I <sub>R</sub>  | Input Leakage Current<br>STB, DS2, CLR, DI <sub>1</sub> -DI <sub>8</sub> Inputs | V <sub>R</sub> = V <sub>CC</sub> Max |         |      |     | 10    | μΑ    |

| I <sub>R</sub>  | Input Leakage Current, MD Input                                                 | $V_R = V_{CC} Max$                   |         |      |     | 30    | μΑ    |

| I <sub>R</sub>  | Input Leakage Current, DS1 Input                                                | $V_R = V_{CC} Max$                   |         |      |     | 40    | μΑ    |

| V <sub>C</sub>  | Input Forward Voltage Clamp                                                     | $I_C = -5 \text{ mA}$                |         |      |     | -1    | V     |

| V <sub>IL</sub> | Input "Low" Voltage                                                             |                                      | DP8212M |      |     | 0.08  | ٧     |

|                 |                                                                                 |                                      | DP8212  |      |     | 0.85  | V     |

| V <sub>IH</sub> | Input "High" Voltage                                                            |                                      |         | 2.0  |     |       | ٧     |

| V <sub>OL</sub> | Output "Low" Voltage                                                            | $I_{OL} = 10 \text{ mA}$             | DP8212M |      |     | 0.45  | V     |

|                 |                                                                                 | $I_{OL} = 15 \text{ mA}$             | DP8212  |      |     | 0.45  | ٧     |

| V <sub>OH</sub> | Output "High" Voltage                                                           | $I_{OH} = 0.5  \text{mA}$            | DP8212M | 3.40 | 4.0 |       | V     |

|                 |                                                                                 | I <sub>OH</sub> = 1.0 mA             | DP8212  | 3.65 | 4.0 |       | ٧     |

| I <sub>SC</sub> | Short-Circuit Output Current                                                    | $V_O = 0V, V_{CC} = 5V$              |         | -15  |     | -75   | mA    |

| I <sub>O</sub>  | Output Leakage Current, High Impedance State                                    | $V_{O} = 0.45 V/V_{CC} Max$          |         |      |     | 20    | μΑ    |

| Icc             | Power Supply Current                                                            |                                      | DP8212M |      | 90  | 145   | mA    |

|                 |                                                                                 |                                      | DP8212  |      | 90  | 130   | mA    |

# $\textbf{Capacitance}^* \; \textbf{F} = 1 \; \text{MHz}, \textbf{V}_{BIAS} = 2.5 \text{V}, \textbf{V}_{CC} = 5 \text{V}, \textbf{T}_{A} = 25 ^{\circ} \text{C}$

| Symbol           | Parameter                                                         | Min | Тур | Max | Units |

|------------------|-------------------------------------------------------------------|-----|-----|-----|-------|

| C <sub>IN</sub>  | DS1, MD Input Capacitance                                         |     | 9   | 12  | pF    |

| C <sub>IN</sub>  | DS2, CLR, STB, DI <sub>1</sub> -DI <sub>8</sub> Input Capacitance |     | 5   | 9   | pF    |

| C <sub>OUT</sub> | DO1-DO8 Output Capacitance                                        |     | 8   | 12  | pF    |

<sup>\*</sup>This parameter is sampled and not 100% tested.

<sup>\*</sup>Derate cavity package 12.7 mW/°C above 25°C; derate molded package 16.0 mW/°C above 25°C.

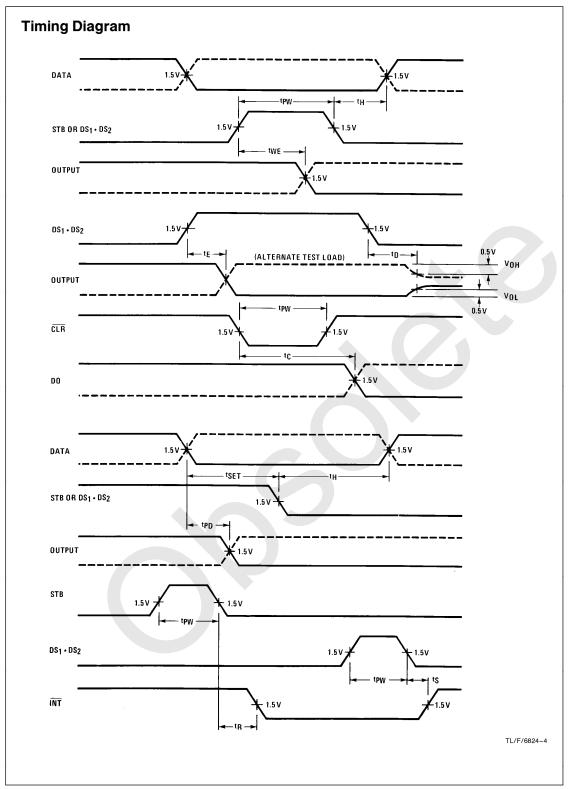

# Switching Characteristics $\mathsf{Min} \leq \mathsf{T}_A \leq \mathsf{Max}, \, \mathsf{Min} \leq \mathsf{V}_{CC} \leq \mathsf{Max}$

| Symbol           | Parameter                    | Conditions | DP8212M |     | DP8212 |     | Units |

|------------------|------------------------------|------------|---------|-----|--------|-----|-------|

| Symbol           |                              |            | Min     | Max | Min    | Max | Omis  |

| $t_{PW}$         | Pulse Width                  |            | 40      |     | 30     |     | ns    |

| t <sub>PD</sub>  | Data to Output Delay         | (Note 1)   |         | 30  |        | 30  | ns    |

| t <sub>WE</sub>  | Write Enable to Output Delay | (Note 1)   |         | 50  |        | 40  | ns    |

| t <sub>SET</sub> | Data Set-Up Time             |            | 20      |     | 15     |     | ns    |

| t <sub>H</sub>   | Data Hold Time               |            | 30      |     | 20     |     | ns    |

| t <sub>R</sub>   | Reset to Output Delay        | (Note 1)   |         | 55  |        | 40  | ns    |

| t <sub>S</sub>   | Set to Output Delay          | (Note 1)   |         | 35  |        | 30  | ns    |

| tE               | Output Enable/Disable Time   | (Note 2)   |         | 50  |        | 45  | ns    |

| t <sub>C</sub>   | Clear to Output Delay        | (Note 1)   |         | 65  |        | 55  | ns    |

Note 1:  $C_L = 30 \ pF$

Note 2:  $C_L = 30 \text{ pF}$  except for DP8212M

$t_{\text{E (DISABLE)}} C_{\text{L}} = 5 \text{ pF}$

# **Switching Conditions**

- 1. Input Pulse Amplitude = 2.5V.

- 2. Input Rise and Fall Times = 5 ns.

- 3. Between 1V and 2V Measurements made at 1.5V with 15 mA & 30 pF Test Load.

- 4.  $C_L$  includes jig and probe capacitance.

- $5. C_L = 30 pF.$

- 6.  $C_L = 30$  pF except for DP8212M  $t_{E\ (DISABLE)}$   $C_L = 5$  pF

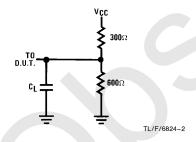

#### Test Load

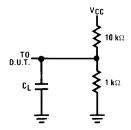

#### Alternate Test Load (Refer to Timing Diagram)

TL/F/6824-3

## **Logic Tables**

#### Logic Table A

| LOGIC TABLE A |    |                                     |                    |  |

|---------------|----|-------------------------------------|--------------------|--|

| STB           | MD | (DS <sub>1</sub> •DS <sub>2</sub> ) | Data Out<br>Equals |  |

| 0             | 0  | 0                                   | TRI-STATE          |  |

| 1             | 0  | 0                                   | TRI-STATE          |  |

| 0             | 1  | 0                                   | DATA LATCH         |  |

| 1             | 1  | 0                                   | DATA LATCH         |  |

| 0             | 0  | 1                                   | DATA LATCH         |  |

| 1             | 0  | 1                                   | DATA IN            |  |

| 0             | 1  | 1                                   | DATA IN            |  |

| 1             | 1  | 1                                   | DATA IN            |  |

CLR resets data latch to the output low state.

The data latch clock is level sensitive, a low level clock latches the data.

Logic Table B

| 9       |                                     |     |    |     |  |

|---------|-------------------------------------|-----|----|-----|--|

| CLR     | (DS <sub>1</sub> •DS <sub>2</sub> ) | STB | Q* | ĪNT |  |

| 0 RESET | 0                                   | 0   | 0  | 1   |  |

| 1       | 0                                   | 0   | 0  | 1   |  |

| 1       | 0                                   | /   | 1  | 0   |  |

| 1       | 1 RESET                             | 0   | 0  | 0   |  |

| 1       | 0                                   | 0   | 0  | 1   |  |

<sup>\*</sup>Internal Service Request flip-flop.

#### **Functional Pin Definitions**

The following describes the function of all the DP8212/DP8212M input/output pins. Some of these descriptions reference internal circuits.

#### INPUT SIGNALS

**Device Select (\overline{DS\_1}, DS\_2):** When  $\overline{DS_1}$  is low and  $DS_2$  is high, the device is selected. The output buffers are enabled and the service request flip-flop is asynchronously reset (cleared) when the device is selected.

**Mode (MD):** When high (output mode), the output buffers are enabled and the source of the data latch clock input is the device selection logic (DS $_1$  • DS $_2$ ). When low (input mode), the state of the output buffers is determined by the device selection logic (DS $_1$  • DS $_2$ ) and the source of the data latch clock input is the strobe (STB) input.

**Strobe (STB):** Used as data latch clock input when the mode (MD) input is low (input mode). Also used to synchronously set the service request flip-flop, which is negative edge triggered.

Data In (DI<sub>1</sub>-DI<sub>8</sub>): Eight-bit data input to the data latch, which consists of eight D-type flip-flops. Incorporating a level sensitive clock while the data latch clock input is high, the Q output of each flip-flop follows the data input. When the clock input returns low, the data latch stores the data input. The clock input high overrides the clear (CLR) input data latch reset.

Clear (CLR): When low, asynchronously resets (clears) the data latch and the service request flip-flop. The service request flip-flop is in the non-interrupting state when reset.

#### **OUTPUT SIGNALS**

Interrupt (INT): Goes low (interrupting state) when either the service request flip-flop is synchronously set by the strobe (STB) input or the device is selected.

Data Out (DO<sub>1</sub>-DO<sub>8</sub>): Eight-bit data output of data buffers, which are TRI-STATE, non-inverting stages. These buffers have a common control line that either enables the buffers to transmit the data from the data latch outputs or disables the buffers by placing them in the high-impedance state.

#### **Connection Diagram**

**Dual-In-Line Package**

TL/F/6824-6

Top View

Order Number DP8212J, DP8212N or DP8212MJ See NS Package Number J24A or N24A

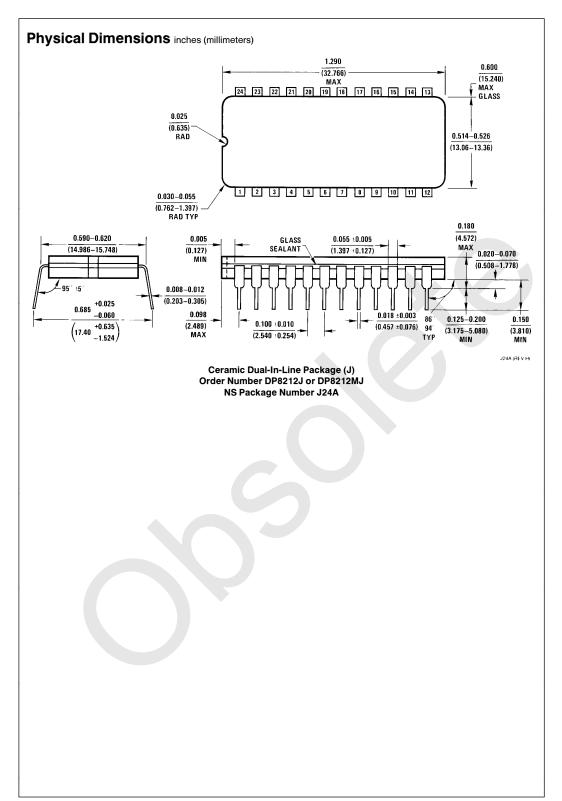

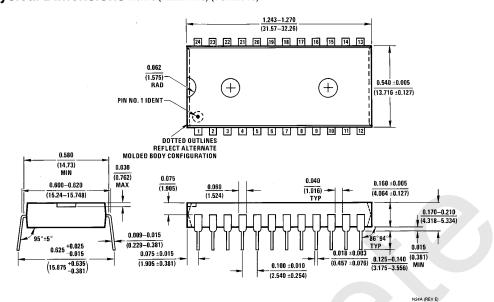

## Physical Dimensions inches (millimeters) (Continued)

Molded Dual-In-Line Package (N) Order Number DP8212N NS Package Number N24A

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018 National Semiconductor Europe

Fax: (+49) 0-180-530 85 86 Email: cnjwge@tevm2.nsc.com Deutsch Tel: (+49) 0-180-530 85 85 English Tel: (+49) 0-180-532 78 32 Français Tel: (+49) 0-180-532 93 58 Italiano Tel: (+49) 0-180-534 16 80 National Semiconductor Hong Kong Ltd. 13th Floor, Straight Block, Ocean Centre, 5 Canton Rd. Tsimshatsui, Kowloon

Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960 National Semiconductor Japan Ltd. Tel: 81-043-299-2309 Fax: 81-043-299-2408

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products | Applications |

|----------|--------------|

|----------|--------------|

Audio www.ti.com/audio Communications and Telecom www.ti.com/communications **Amplifiers** amplifier.ti.com Computers and Peripherals www.ti.com/computers dataconverter.ti.com Consumer Electronics www.ti.com/consumer-apps **Data Converters DLP® Products** www.dlp.com **Energy and Lighting** www.ti.com/energy DSP dsp.ti.com Industrial www.ti.com/industrial Clocks and Timers www.ti.com/clocks Medical www.ti.com/medical Interface interface.ti.com Security www.ti.com/security

Logic logic.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Power Mgmt power.ti.com Transportation and Automotive www.ti.com/automotive

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID <u>www.ti-rfid.com</u>

OMAP Mobile Processors www.ti.com/omap

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>

TI E2E Community Home Page <u>e2e.ti.com</u>